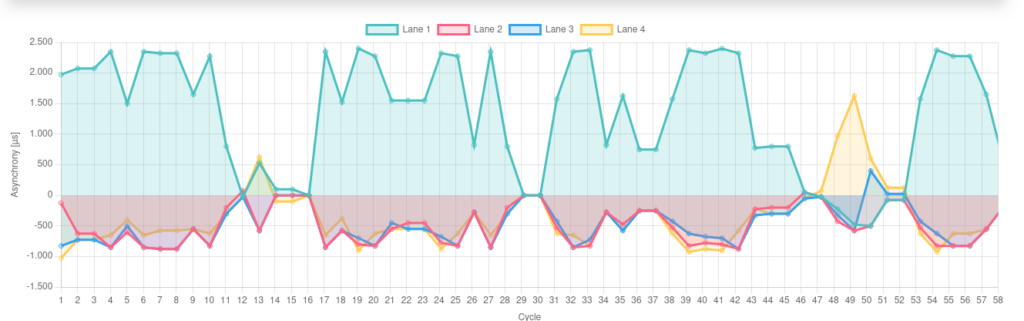

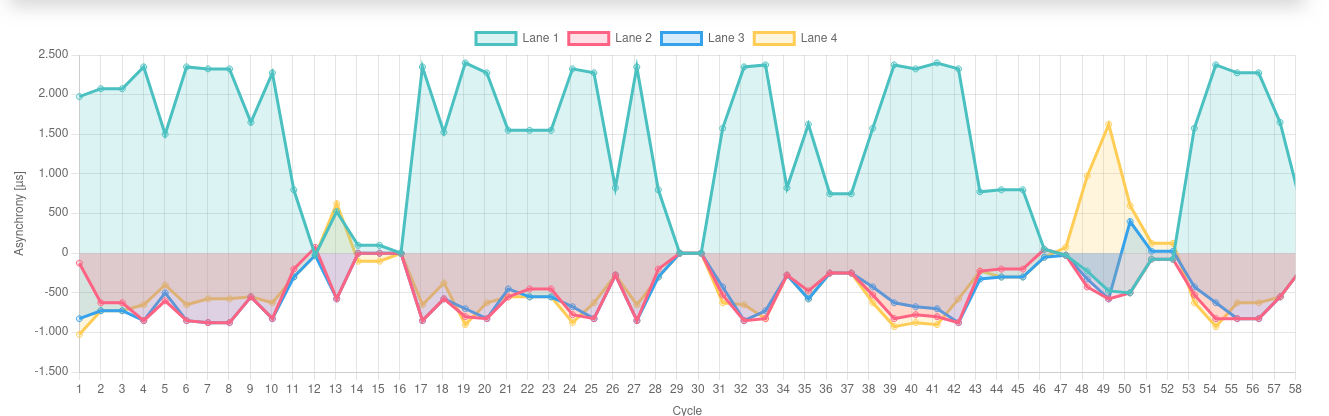

With the latest addition, we can now perform asynchrony investigation.

The quaduino lanes send a discrete signal to the control arduino, that measures the module time at which the discrete is received via interrupt.

Here, computing lane 1 behaves strangely, so we will investigate if that is a bug or any other suspicious behaviour. This is independent from the control arduino (we switched connectors) and thus must be an issue with lane #1 (the uppermost).

Generally, the lanes are quite close to synchrony after we performed the xsynchro service (except lane #1). Most of the time, the other lanes are within 100µs synchronous. Lane 1 raises the limit to about 3ms.

Schreibe einen Kommentar